Компания IBM на конференции Hot Chips 2024 в Пало-Альто (Калифорния, США) анонсировала процессор Telum II и ускорители Spyre. Оба продукта будут использоваться в мэйнфреймах нового поколения IBM Z для ИИ-задач.

Процессор Telum II, разработанный с использованием 5-нанометровой технологии Samsung, предлагает восемь высокопроизводительных ядер с тактовой частотой 5,5 GHz. Каждое ядро оснащается L2-кэшем объемом 36 Mb, что примерно на 40% выше, чем у чипов предыдущего поколения. Объем виртуальной кеш-памяти L3 и L4 увеличен до 360 Mb и 2,88 Gb соответственно. Энергопотребление снизилось на 15%.

Также есть интегрированный ИИ-ускоритель, специализированный для ускорения операций ввода-вывода. Новый блок ускорения ввода-вывода DPU разработан для улучшения обработки данных с 50-процентным увеличением плотности ввода-вывода. Подсистема предлагает 192 линии PCI Express 5.0 (5 x 16 линии), которые можно вывести на 16 слотов. Ожидается, что вычислительная мощность каждого ускорителя достигнет 24 TOPS.

Архитектура ускорителя оптимизирована для работы с большими языковыми моделями и поддерживает широкий спектр ИИ-моделей для комплексного анализа структурированных и текстовых данных. Кроме того, новый процессор поддерживает тип данных INT8 для повышения эффективности вычислений. При этом на системном уровне Telum II позволяет каждому ядру процессора получать доступ к любому из восьми ИИ-ускорителей в рамках одного модуля, обеспечивая более эффективное распределение нагрузки и достигая общей производительности в 192 TOPS.

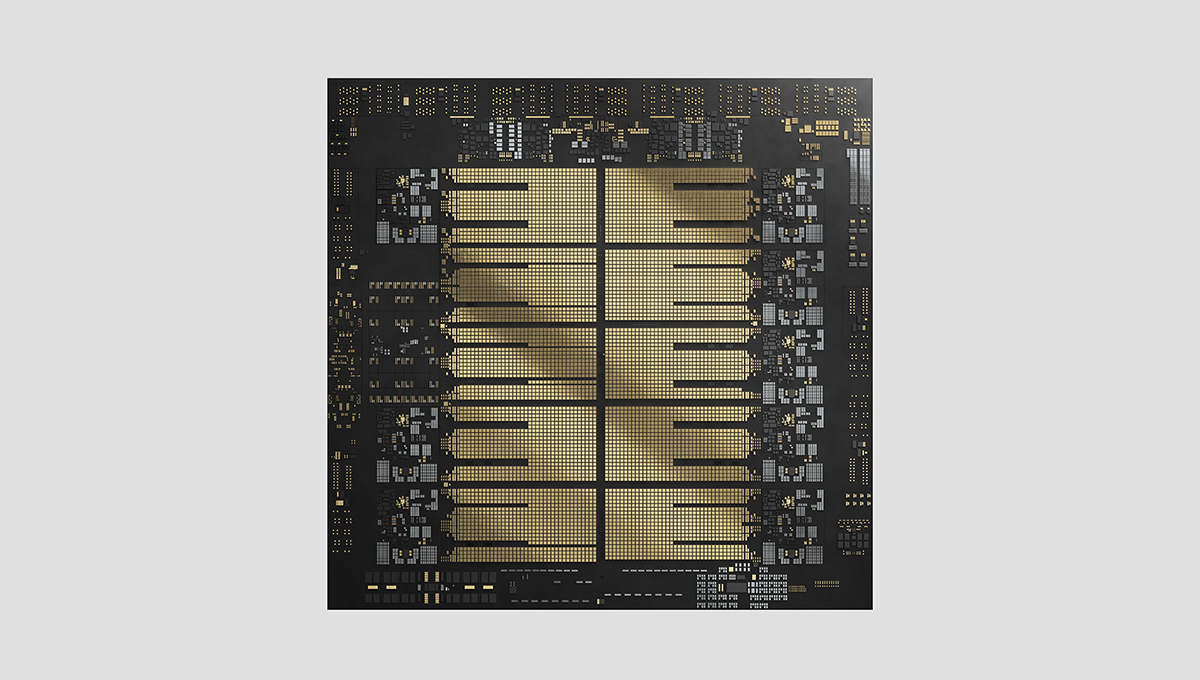

IBM также анонсировал ускоритель Spyre — это чип с 32 ядрами, архитектура которых схожа с архитектурой ускорителя, интегрированного в чип Telum II. Несколько таких ускорителей могут быть подключены к подсистеме ввода-вывода IBM Z посредством PCIe. При этом TDP одного ускорителя составляет всего 75 Вт. Ускоритель содержит 128 Gb памяти LPDDR5, о производительности IBM не говорит.

Telum II и Spyre разработаны для поддержки широкого спектра сценариев использования ИИ. Оба продукта поступят в продажу в 2025 году.